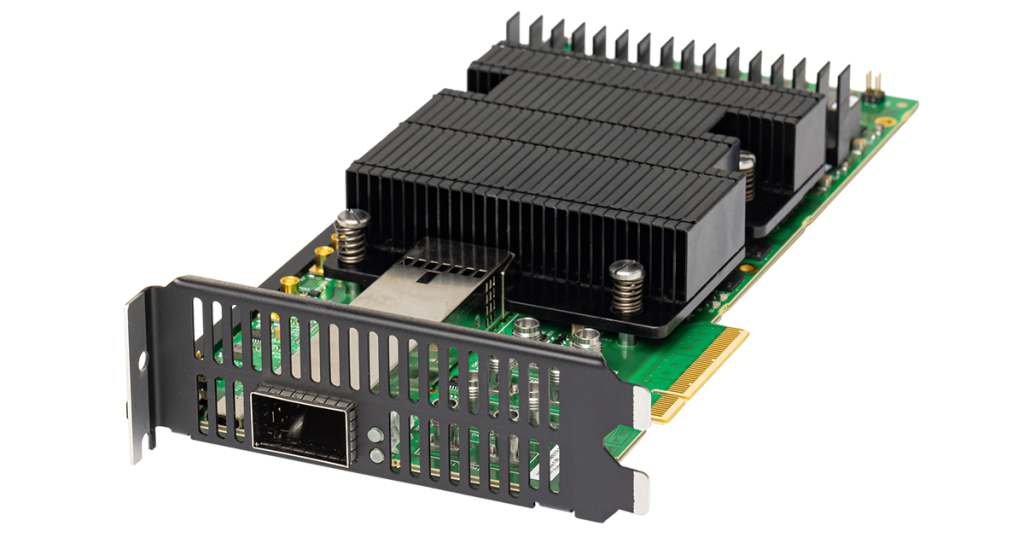

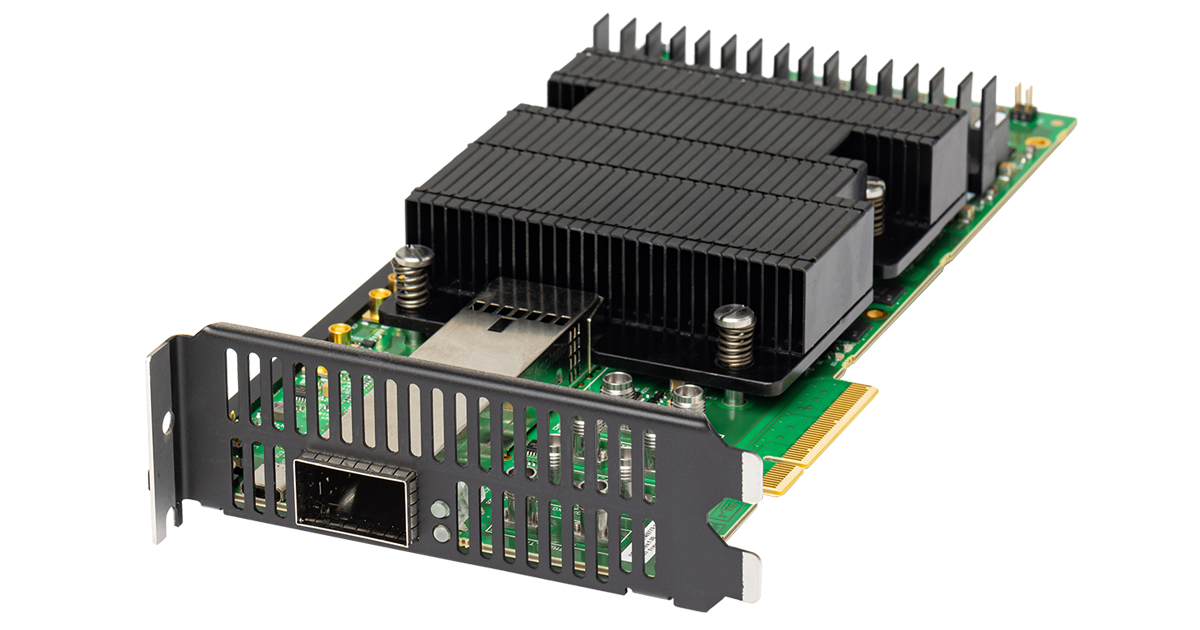

Freya-800G-4S-1P-OSFP

Freya-800G-4S-1P-OSFP

Xena Freya-800G-4S-1P-OSFP は、4つの Ethernet メディアレート (800Gbps, 400Gbps, 200Gbps, 100Gbps) に対応した ValkyrieBay 用テストモジュールです。

特徴

- 4種類の Ethernet メディアレートに対応 (1x 800Gbps, 2x 400Gbps, 4x 200Gbps, 8x 100Gbps)

- 112G SerDes 対応

- オートネゴシエーション&リンクトレーニング(AN/LT)

- 3年間のハードウェア保証・ソフトウェアアップデートービスを提供

| ポート仕様 | |

|---|---|

| 対応メディアレート | OSFP : 800Gbps, 400Gbps, 200Gbps, 100Gbps |

| テストポート数 | 1x 800GbE, 2x 400GbE, 4x 200GbE, 8x 100GbE |

| インターフェースオプション |

OSFP ケージ

|

| オートネゴシエーション、リンクトレーニング機能 | IEEE 802.3 Clause 73, Consortium 800G specification, Auto-negotiation IEEE 802.3 Clause 72, Link training |

| Forward Error Correction (FEC) | RS-FEC (Reed Solomon) (544,514,t=15), IEEE 802.3 Clause 119, Clause 134 |

| トランシーバ数 | 1 x OSFP |

| ポート統計機能 | リンクステート、FCSエラー、ポーズフレーム、ARP/PING、エラー挿入、トレーニングパケット |

| フレーム間隔(IFG) | 16~56byte(デフォルト20byte: 8Bプリアンブル(SFDを含む)+12B IFG) |

| 送信ラインレート | アイドルギャップを強制する事で透過的に-1,000ppm(-10ppm単位)までラインレートを調整可能 |

| 送信ラインクロック | -400~400ppm(1ppmステップ)の範囲で調整可能(全ポート共有) |

| ARP / PING | ポート毎にIP,MACアドレスを設定可能 |

| フィールドアップグレード | FPGAファームウエア、操作用ソフトウエア共に完全対応 |

| ヒストグラム統計 | ポート毎の2つのリアルタイムヒストグラム。各ヒストグラムはRX/TXパケット長、全トラフィック、または特定のトラフィックに対する遅延分布。フィルター機能を提供 |

| TX無効機能 | TXポートのリンクを無効にする事が可能 |

| IGMPv2マルチキャスト機能 | IGMPv2を用いたマルチキャストへの連続的な参加が可能。期間を変更できるインターバル設定付き |

| ヒストグラム統計 | ポート毎の2つのリアルタイムヒストグラム。各ヒストグラムはRX/TXパケット長、全トラフィック、または特定のトラフィックに対する遅延分布。フィルター機能を提供。 |

| ループバックモード |

|

| 発振器特性 |

|

| PCS/PMAレイヤ | |

| ペイロードテストパターン | PRBS-31Q |

| アラーム | PRBSパターンロス、リンクシンクロス |

| エラー解析 | ビットエラー:秒、カウント、レート |

| PCS仮想レーン構成 | ユーザー定義のスキューをTx仮想レーンごとに発生 また再配置機能のテストのための、ユーザ定義仮想レーンへのSerDesマッピング |

| PCSバーチャルレーン統計 | 相対的なバーチャルレーンスキュー計測(2048bit迄)、補正ビットエラー、PreFEC BER |

| FEC 総合統計 | 総補正FECシンボル、補正なしFECシンボル、推定Pre-FEC BER、推定Post-FEC BER、Pre-FECエラー分布グラフ |

| リンクフラップ | ミリ秒(ms)単位での精度を保った単発または継続的なリンクダウン |

| エラーインジェクション (PMA Layer) |

単発でのビットエラーやバーストエラーの挿入や、継続的なエラー挿入 |

| PHY/トランシーバ | |

| プログラマブル・パターン・ジェネレーター | FCS付きイーサネットフレーム、トラフィック負荷:最大100%まで、設定可能なフレームサイズの分布と内容、送受信統計 |

| PHYアドバンスト機能 | |

| イコライザーコントロール | Tx 送信イコライザーコントロール

Rxイコライザー/CTLEのオートチューニング |

| シグナルインテグリティ解析 | FEC訂正チャート、シグナルインテグリティの詳細表示 |

| 送信エンジン | |

| ポート毎のストリーム数 | 256個(ワイヤスピード) |

| ストリーム毎のテストペイロード挿入 | タイムスタンプ、シーケンス番号、データ完全性シグネチャを含むワイヤスピードのパケット生成 オプションで各パケットに挿入可能。 |

| ストリーム統計 | TX Mbit/s、packets/s、パケット数、バイト数、FCS エラー |

| 帯域幅プロファイル | バーストサイズ及び密度を定義。ユニフォームとバースト的な帯域幅プロファイルストリームは交互に配置が可能 |

| フィールドモディファイヤー | 値の増加、減少、ランダム化が可能な16bitフィールドまたは32bitフィールド変更機能。各フィールド変更機能は、設定可能なビットマスク、繰り返し、最小、最大、ステップパラメータを包含。 ストリーム毎に8個(16bit)/4個(32bit)のフィールド変換機能を使用可能。 |

| パケット長制御 | パケット長の固定、ランダム、バタフライ、増長が可能。 パケット長は56byte~12288byteまで対応。 |

| パケットペイロード(basic) | ユーザ定義の1~18byteパターン、8bitインクリメントパターンの繰り返し使用が可能 |

| エラー生成 | 最小56byte最大12288byteのパケット長、シーケンス挿入、順番違い、ペイロード完全性、FCSエラーを生成可能 |

| TXパケットヘッダー及びRXデコード機能 | Ethernet、Ethernet II、VLAN、ARP、IPv4、IPv6、UDP、TCP、LLC、SNAP、GTP、ICMP、RTP、RTCP、STP、MPLS、PBB、及びユーザー定義 |

| パケットスケジュールモード |

|

| 受信エンジン | |

| ポート毎にトレース可能なストリーム数 | 2016(ワイヤースピード) |

| 受信パケットのテストペイロード自動検知機能 | レイテンシ、ロス、ペイロード完全性、シーケンスエラー、順番違いのチェックや分析のリアルタイムな報告 |

| ジッター計測 | MEF10に準拠したジッター(パケット遅延変動)計測。8nsの確度で32ストリームまで計測可能 |

| ストリーム統計 |

|

| 遅延計測確度 | ±32 ns |

| 遅延計測分解能 | 8 ns(遅延計測は校正可能であり、トランシーバモジュールからの遅延を除去可能) |

| フィルター数 |

|

| フィルター統計 | フィルタ毎:RX Mbit/s、パケット/s、パケット数、バイト数 |

| キャプチャ | |

| キャプチャ機能 | 全てのトラフィック、ストリーム、FCSエラー、フィルタマッチ、またはテストペイロードを除くトラフィック |

| キャプチャ可能な パケットサイズ | 16~12288bytes |

| ポート毎のワイヤースピードキャプチャバッファ | 100GEで96 kB |

| 低速キャプチャバッファ(10Mbit/speed) | 4096パケット |

| ハードウェア仕様 | |

| 消費電力 | TBA |

| 重量 | 2.31 lbs (1.05 kg) |

| 環境 | 動作温度:10~35℃。保存温度:-40~70º℃。湿度:8%~90% |

| 規制 | FCC (米国)、CE (欧州) |

| 注意事項 | このモジュールはVal-C12-2400シャーシでのみサポート。Val-C12-2400シャーシに2つのスロット使用。 |